關(guān)于我們

ABOUT US

瑞安市永信機(jī)械有限公司座落于“中國(guó)包裝機(jī)械城”之稱的浙江省瑞安市,是一家集研發(fā)、制造、銷售于一體的科技型機(jī)械企業(yè)。

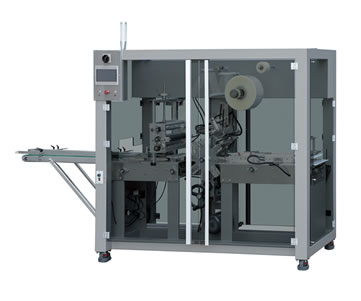

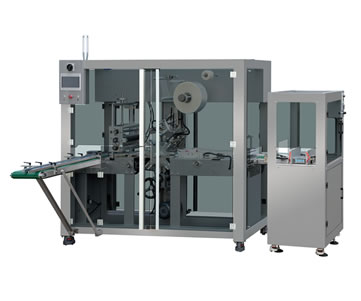

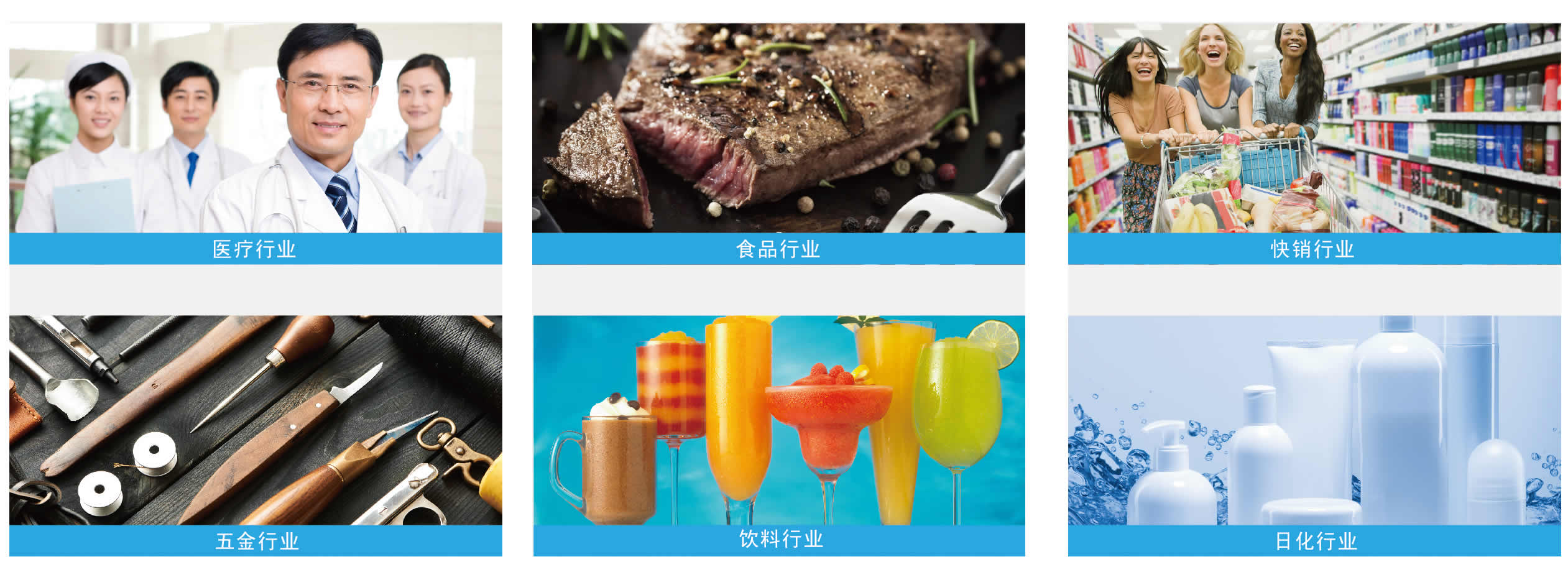

永信機(jī)械歷經(jīng)十多年不斷創(chuàng)新的發(fā)展歷程,先后榮獲多項(xiàng)國(guó)家發(fā)明及實(shí)用新型證書,所有產(chǎn)品均通過歐盟安全“CE”認(rèn)證。公司專業(yè)生產(chǎn)透明膜三維包裝機(jī)、熱收縮包裝機(jī)、裝盒機(jī)、封箱機(jī)等系列產(chǎn)品及包裝材料。產(chǎn)品廣泛應(yīng)用于醫(yī)藥、食品、化妝品、日用品、文具用品等領(lǐng)域。憑借可靠的質(zhì)量、穩(wěn)定的性能和周到的售后服務(wù),使產(chǎn)品遍布全國(guó)各省市自治區(qū)的同時(shí),還遠(yuǎn)銷海外國(guó)際市場(chǎng),深受國(guó)內(nèi)外用戶的好評(píng)。

.... 查看更多 >>